توضیحات

عنوان فارسی: مقسم دینامیکی-منطقی فرکانس(تقسیم کننده فرکانس) برای ترکیب کننده فرکانس شبکه بی سیم 5گیگا هرتز

عنوان انگلیسی مقاله ترجمه شده:

A Dynamic-Logic Frequency Divider for 5-GHz WLAN Frequency Synthesizer

چکیده:

در این مقاله یک مقسم دینامیکی-منطقی فرکانس برای ترکیب کننده فرکانسی CMOS یکپارچه ارائه می شود.تقسیم کننده بر پایه دو مدول و مدار دینامیک-منطقی برای کاهش توان مصرفی ،تعداد ترانزیستور و سطح تراشه طراحی شده است.نتایج شبیه سازی نشان می دهد که،هدف این مدار دستیابی به باند فرکانسی عملی از 5.825-5.155 گیگا هرتز برای کاربردهای شبکه بی سیم محلی می باشد.این مقسم تحت ولتاژ تغذیه v1.8 ،توان مصرفی 3.6mw و سطح تراشه 0.285mm2 می باشد.

کلمات کلیدی: مقسم،دینامیکی-منطقی،مقسم دومدول،ترکیب کننده فرکانسی

1.مقدمه

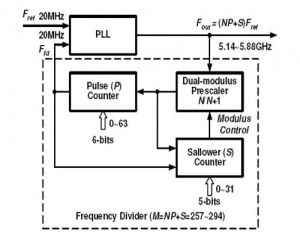

IEEE802.11a وHiperLAN ،استانداردهای شبکه داده های بی سیم با ناحیه فرکانس عملی 5تا 60 گیگا هرتز ،که 15 کانال با فاصله 20مگاهرتز را پوشش می دهد ؛می باشد[1].ترکیب کننده فرکانسی به طور گسترده ای برای تولید سیگنال های نوسان محلی(LO) در سیستم های ارتباطی مدرن مورد استفاده می باشد.به منظور پوشش مورد نیاز حمل و عملکرد فرکانس ورودی از 5 گیگا هرتز، بخش های مقسم باید از 257تا294 برنامه ریزی شود.ناحیه فرکانسی یک ترکیب کننده فرکانسی به وسیله مقسم فرکانسی و همچنین کنترل ولتاژ نوسان ساز محدود می گردد.برای استاندارد WLAN رایج ترین فرکانس سرعت بالا بر پایه پالس جلو رونده طراحی شده است.[2,6]این حالت معمولا ازیک مقسم دو مدول (DMP) ،یک شمارنده پالس 6بیتی (P) و یک شمارنده 5 بیتی sallower،تشکیل شده است.دو شمارنده،محدوده تقسیم داده شده ی مقسم، را تولید می کنند و با مقدار DMP تقسیم می کند.برای نگه داشتن فرکانس بالای ورودی و کاهش توان مصرفی DMP بین سرعت و تقسیم با مقدار مبادله می کند.از سوی دیگر طراحی ها نیاز به دو شمارنده اضافی برای تولید نسبت تقسیم مورد نظر دارد.این روش نیاز به تعداد زیادی گیت شمارش ،سطح تراشه بزرگ و توان مصرفی بالا دارد.این مقاله یک مقسم فرکانسی با همان عملکرد بدون استفاده از شمارنده sallower،برای کاهش توان مصرفی و سطح تراشه غیرضروری پیشنهاد می دهد.

2.ساختار مقسم فرکانسی

2.1.ساختار پالس جلورونده

شکل (1) ساختار یک مقسم که بر اساس آن توپولوژی پالس جلورونده طراحی شده است را نشان می دهد.DMP ابتدا فرکانس بالای ورودی را به N+! سیگنال مدول پایین تقسیم می کند.سپس شمارنده sallower،پالس خروجی DMP را می شمارد،سپس سیگنال مدول را به بالا(HIGH) تبدیل می کند و پس از آن DMP تقسیم را با N شروع می کند.خروجی DMP، همزمان توسط شمارنده پالس شمرده می شود.شمارنده پالسی،شمارنده sallower را بعد از خروجی پالس بازنشانی می کند.بنابراین نسبت تقسیم کل به طریق زیر بدست می آید:

که در این رابطه N=عدد تقسیم DMP

P=عدد شمارنده پالسی

S=عدد شمارنده sallower

می باشد.

شکل1.بلوک دیاگرام مقسم DMP ساده

برای استاندارد WLAN ،فرکانس ها به گروه تقسیم می شود.در باند پایین (5.15-5.35GHZ) ،PوN به ترتیب 33 و 8می باشد.تا زمانی که S بین 1تا 12 باشد نسبت تقسیم کلی بین 257تا268 برای مرحله اول می باشد.

از سوی دیگر ،در باند بالا (5.725-5.825GHZ)،P=34 می باشد و تا زمانی که S بین 13تا 22 باشد.نسبت تقسیم کل از 285تا 294 است.مشاهده می گردد که ساختار نشان داده شده در شکل (1) برخی اشکالات قابل توجهی دارد.یک مقسم فرکانسی معمولی به دو شمارنده اضافی برای تولید نسبت تقسیم داده شده،نیاز دارد.به منظور پوشش گشترده تر محدوده فرکانس LO ،شمارنده پالسی باید کمی بیت بیشتری را گسترش دهدو این سبب افزایش سطح تراشه و توان مصرفی می گردد.

توجه:

- برای دانلود فایل word کامل ترجمه از گزینه افزودن به سبد خرید بالا استفاده فرمایید.

- لینک دانلود فایل بلافاصله پس از خرید بصورت اتوماتیک برای شما ایمیل می گردد.

به منظور سفارش ترجمه تخصصی مقالات خود بر روی کلید زیر کلیک نمایید.

سفارش ترجمه مقاله

نقد و بررسیها

هنوز بررسیای ثبت نشده است.