توضیحات

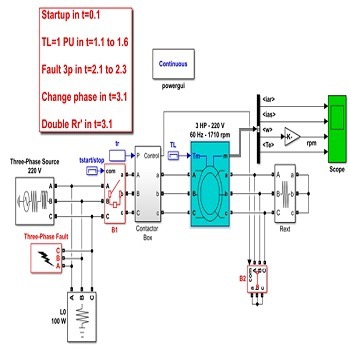

پروژه شبیه سازی یک رگولاتور با افت ولتاژ پایین دیجیتال با روش تنظیم coarse-fine و عملکرد Burst-mode با سیمولینک

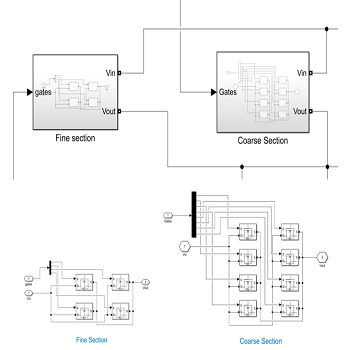

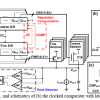

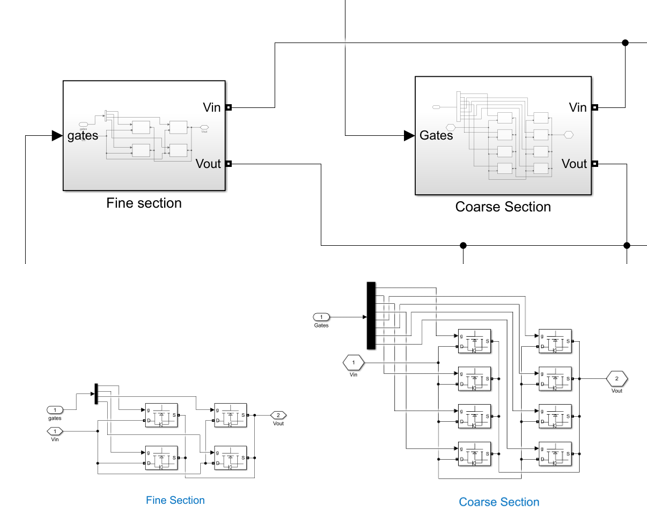

آرایه های ترانزیستوری (Coarse and Fine sections)

به منظور ساده سازی شبیه سازی به جای آرایه های 64 ترانزیستوری در بخش Coarse و 32 ترانزیستوری در بخش Fine، آنها را به ترتیب با 8 و 4 ترانزیستور شبیه سازی کرده ایم.

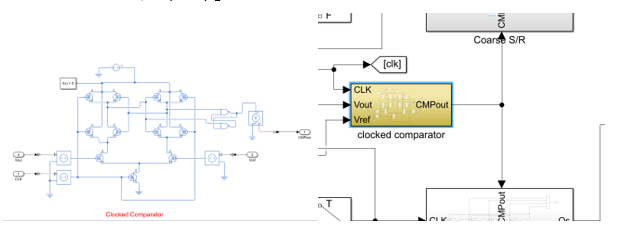

S/R shift registers

برای هر یک از بخش ها یک شیفت رجیستر که سیگنال گیت ها را به وجود می آورد طراحی شده است. شیفت رجیستر Coarse شامل 8 عدد d-flip flop و مالتیپلکسر برای به وجود آوردن 8 سیگنال گیت و شیفت رجیستر Fine شامال 4 عدد d-flip flop و مالتیپلکسر برای به وجود آوردن 4 سیگنال گیت می باشند.

چکیده مقاله (ترجمه ماشینی)

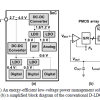

تنظیم کننده افت فشار دیجیتال (D-LDO) اخیراً بخاطر عملکرد ولتاژ پایین و مقیاس پذیری فرایند مورد توجه واقع شده است. با این حال ، معامله بین کارایی فعلی و سرعت پاسخ گذرا ، کاربردهای آن را محدود کرده است. در این کار ، یک روش تنظیم دقیق (CFT) با عملکرد حالت انفجار به D-LDO پیشنهاد شده است. به محض اینکه ولتاژ undershoot / overshoot تشخیص داده شد ، تنظیم درشت سریعاً متوجه کلمه کنترل درشتی می شود که جریان بار باید در آن قرار داشته باشد ، با قدرت MOS قدرت زیاد و فرکانس نمونه برداری بالا برای مدت زمان ثابت. سپس ، تنظیم دقیق ، با کاهش قدرت MOS قدرت و فرکانس نمونه برداری ، D-LDO را به ولتاژ خروجی مورد نظر تنظیم می کند ، و برای دقت بالا و بازده جریان ، عملکرد حالت پایدار را بر عهده می گیرد. D-LDO پیشنهادی در یک فرآیند CMOS 65 نانومتری با منطقه فعال 0.01-mm2 تأیید می شود. زیر شلیک و ولتاژ اندازه گیری شده به ترتیب 55 و 47 میلی ولت است که دارای مراحل بارگیری 2 تا 100 میلی آمپر با زمان لبه 20 نانومتری است. جریان سکون 82 میکرومولار است که رقم شایستگی 0.43-ps (FOM) حاصل شده است. و سرعت ردیابی مرجع 1.5 ولت در میکرو ثانیه است.

برای دستیابی به یک راه حل مدیریت قدرت با دقت بالا و کارایی بالا برای یک سیستم بر روی تراشه (SoC) همانطور که در شکل 1 (الف) نشان داده شده است ، تنظیم کننده های افت تحصیلی کم (LDOs) به طور گسترده ای به عنوان تنظیم کننده های پس از DC-DC استفاده می شوند مبدل ها LDO آنالوگ (A-LDO) می تواند به پاسخ گذرا سریع و ایمنی موج دار در ولتاژهای ورودی بالا ، به عنوان مثال 1.2 ولت دست یابد [1]. با این حال ، برای سیستم های کم مصرف ، ولتاژ ورودی LDO ممکن است به 0.6 ولت کاهش یابد ، در این صورت طراحی تقویت کننده خطا در A-LDO معمولی ممکن است دشوار باشد.

پروژه شبیه سازی یک رگولاتور با افت ولتاژ پایین دیجیتال با روش تنظیم coarse-fine و عملکرد Burst-mode با سیمولینک توسط کارشناسان گروه ۱.۲.۳ پروژه پیاده سازی گردیده .

- فایلهای پروژه به صورت کامل پس از خرید فایل بلافاصله در اختیار شما قرار خواهد گرفت.

دیدگاهها

هیچ دیدگاهی برای این محصول نوشته نشده است.